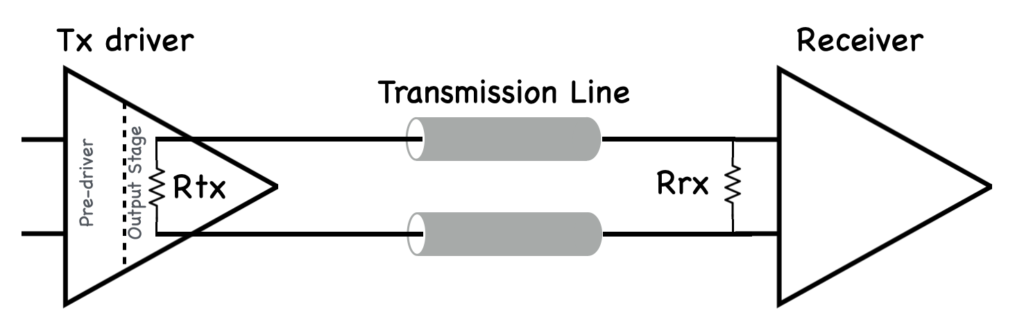

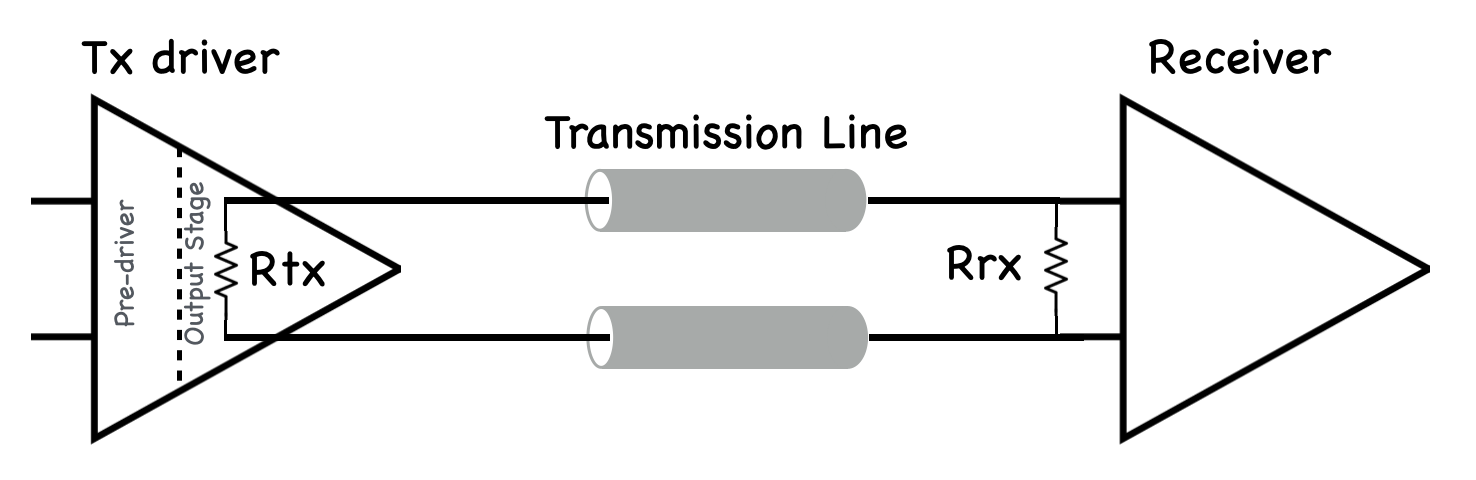

高速通信では差動シリアル通信が一般的であり、以下の図に示すように主にトランスミッター(Tx Driver)、伝送線路、レシーバー、送受信側の終端抵抗から構成されます。

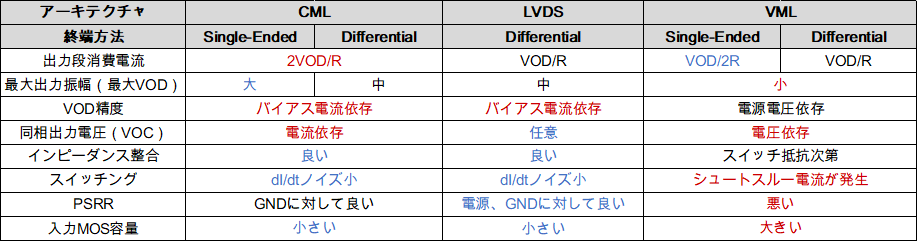

Tx Driverのアーキテクチャの代表的なものとしてはCML、LVDS、VMLが挙げられます。

これらは出力振幅などについての規格を表す用語としても用いらるようですが、ここではそれぞれの回路構成に着目して特徴や設計の要所などをまとめます。

目次

各アーキテクチャ共通の特徴

Tx Driverをさらに細かくみると、出力段、終端抵抗、Pre-driverが主な構成要素となっています。

CML、LVDS、VMLというのは終端抵抗を含む出力段のアーキテクチャであり、電流駆動型(CML、LVDS)と電圧駆動型(VML)に分類されます。いずれのアーキテクチャにおいても伝送線路での反射を防ぐためには出力段の出力インピーダンスを伝送線路の特性インピーダンスと一致させる必要があります(インピーダンス整合)。これが各アーキテクチャでの終端方法、ひいては振幅やコモン電圧などへの制約となります。

Pre-driverは出力段を駆動する役割を担っています。出力段のMOSスイッチをデータレートに合った速度で切り替えられるよう十分な駆動力が必要であり大きな電流を流します。データレートに比例した電流が流れるため高速になるほど消費電流への寄与が大きくなります。

なお、以下では伝送線路の特性インピーダンス50ohmsとして各抵抗値を考えています。

CML (Current Mode Logic)

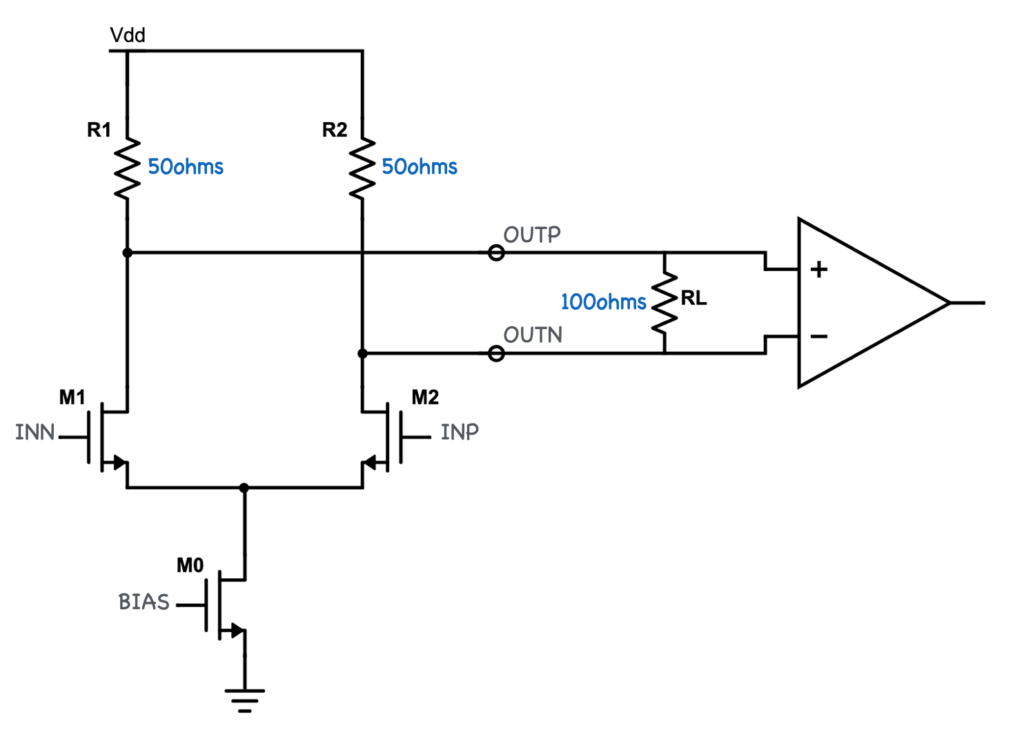

CML(Current Mode Logic)は電流駆動型のDriverです。

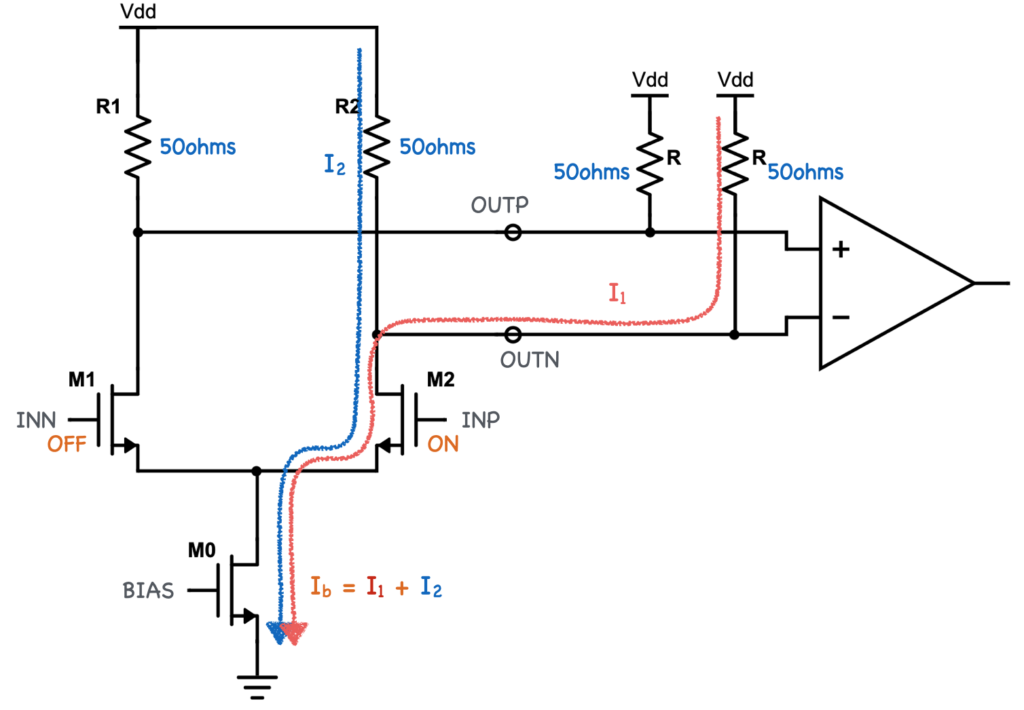

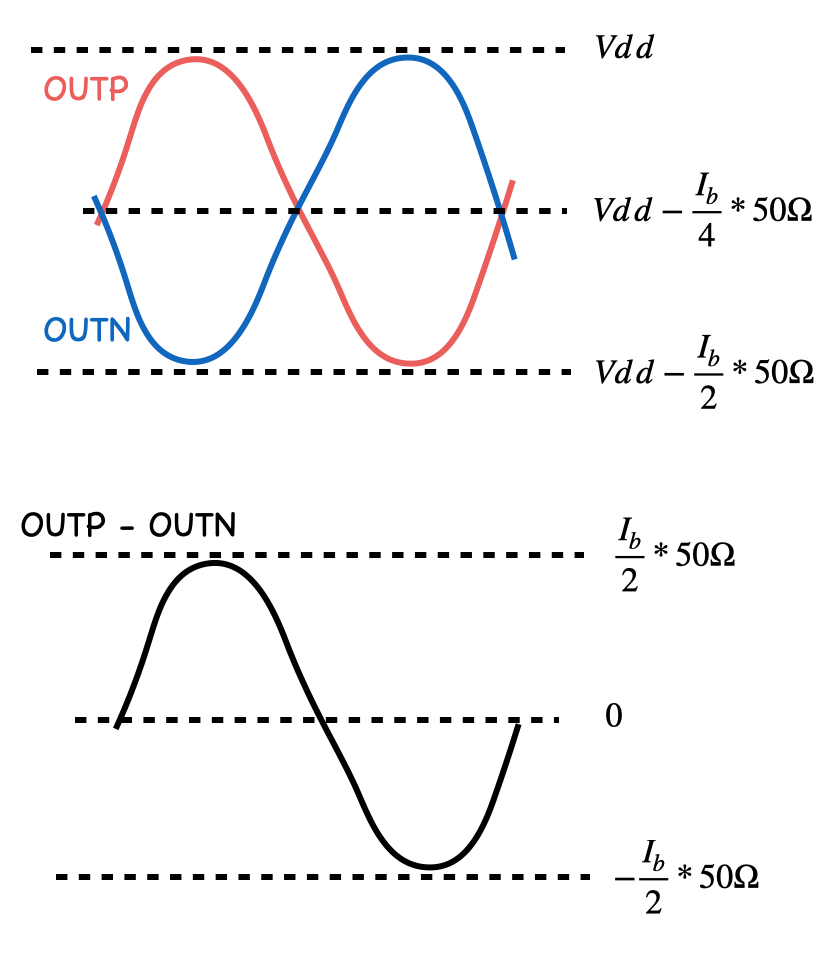

下図の$M0$が電流源として動作し、$M1$、$M2$はスイッチとして動作します。スイッチを切り替えることで受信側終端抵抗$R_L$に流れる電流の方向が反転し、差動出力電圧$V_{OD}=OUTP-OUTN$が発生します。

$R_1$、$R_2$がそれぞれシングルエンド50ohmsの出力抵抗として見えることでインピーダンス整合が取れています。

CMLの受信側終端方法はSingle-Ended TerminationとDifferential Terminationの両方を適用可能です。

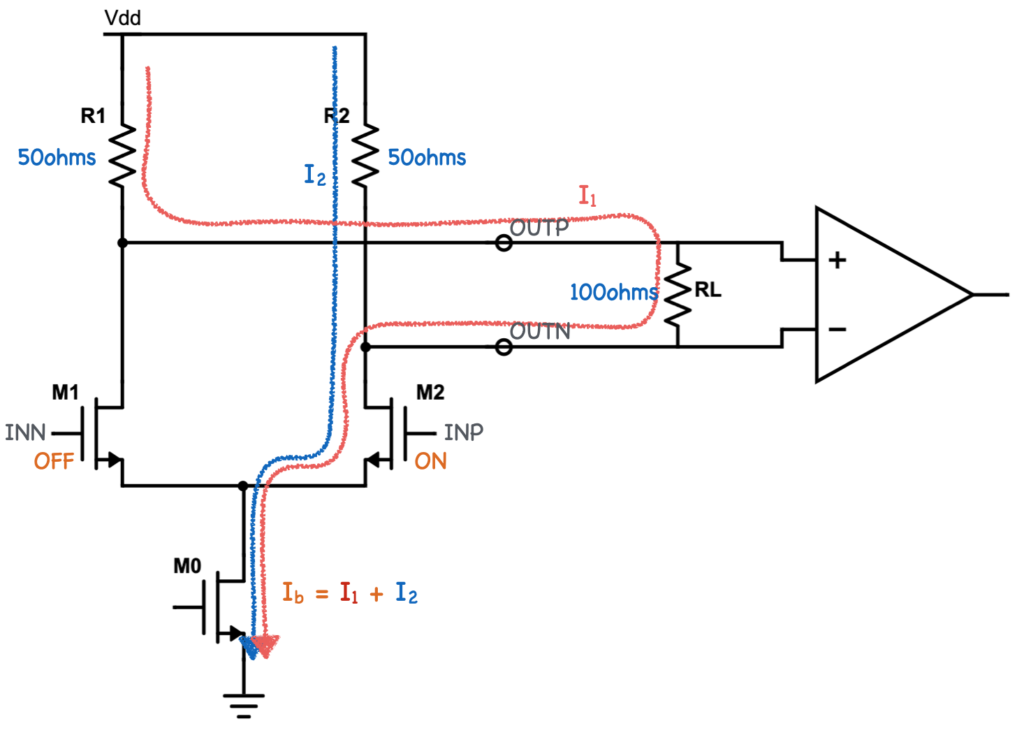

Differential Termination

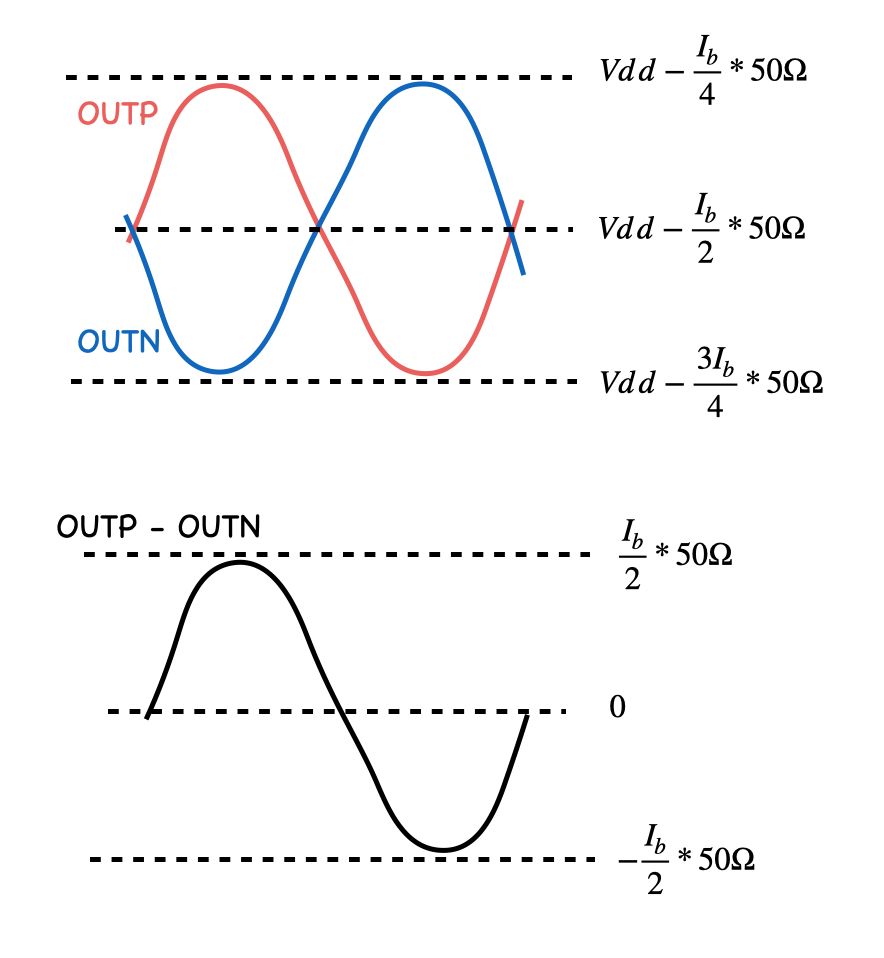

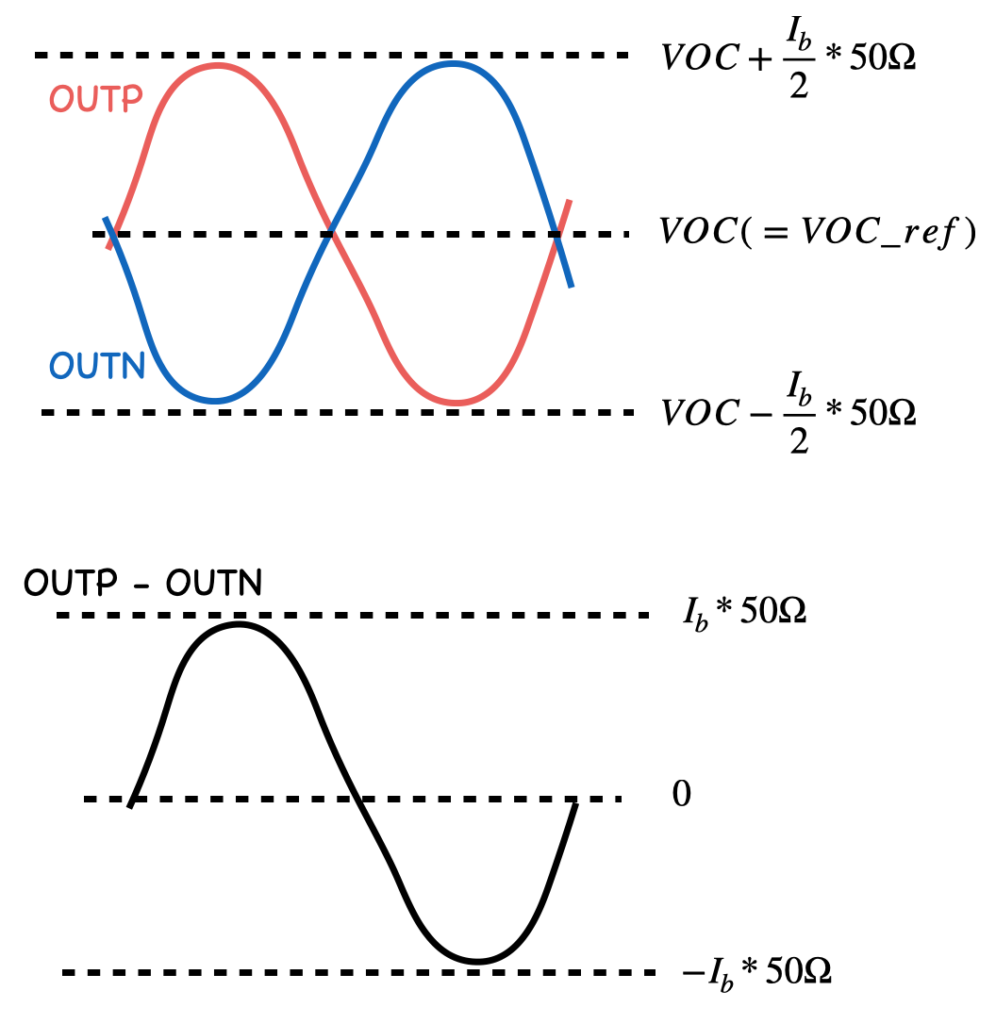

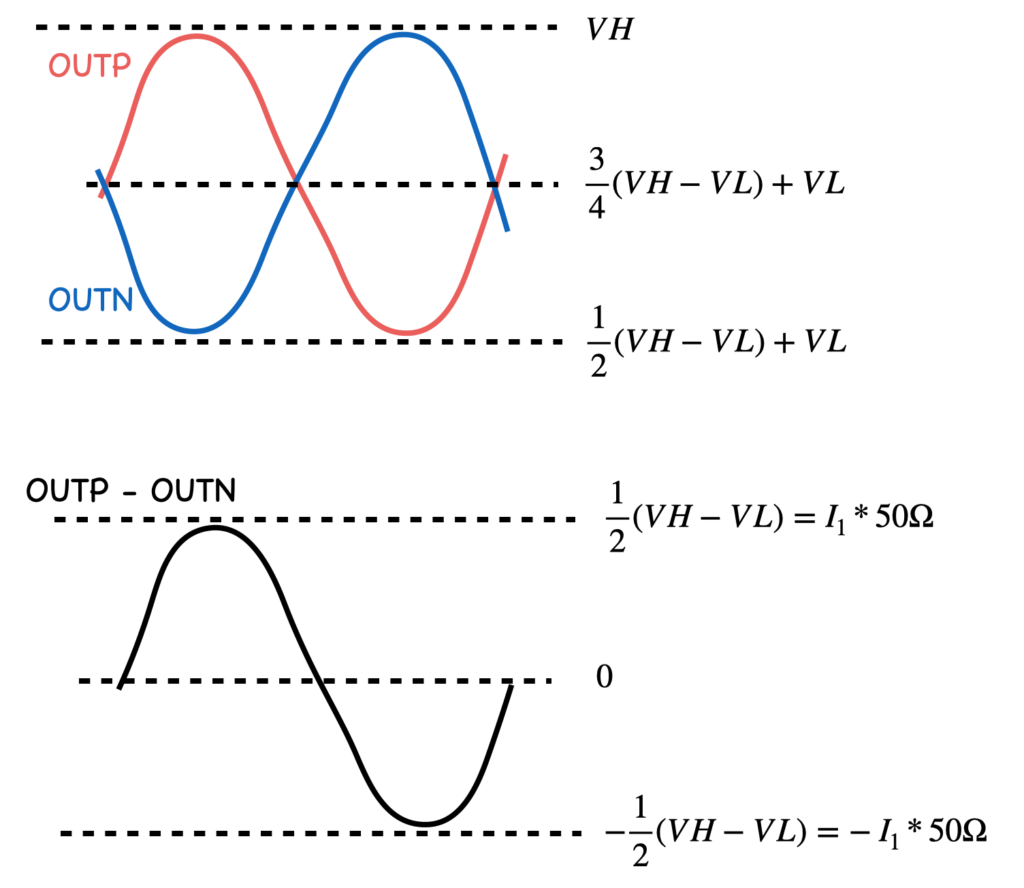

下図のようにバイアス電流$I_b$が$R_1+R_L=150\Omega$と$R_2=50\Omega$で分流され、$I_1*R_L=\frac{I_b}{4}*2*50\Omega$が出力の差動振幅となります。差動出力振幅、同相出力電圧ともに$I_b$に依存します。

Single-Ended Termination

Single-Ended TerminationではDifferential Terminationと比べて同相出力電圧$V_{OC}$を高くすることができ、電流源の動作点を確保しやすいです。そのためバイアス電流を増やすことで出力振幅を大きくすることが容易です。

上記を含めCMLには以下の特徴があります:

- 出力振幅は$V_{OD}=\frac{I_b}{2}*50\Omega$で、出力振幅に対しての消費電流が大きい。

- 定電流のため$dI/dt$ノイズが小さい。

- 同相出力電圧が高く電流源の動作点確保が容易かつ電流駆動のため大きい出力振幅が得られる。

- 内部抵抗$R1$、$R2$が出力抵抗として見えるのでインピーダンス整合が取りやすい。

- 出力段電流$I_b$の値によって$V_{OC}$が決まってしまう。

- 差動出力振幅に直接影響するためバイアス電流の精度が重要。

LVDS (Low Voltage Differential Signaling)

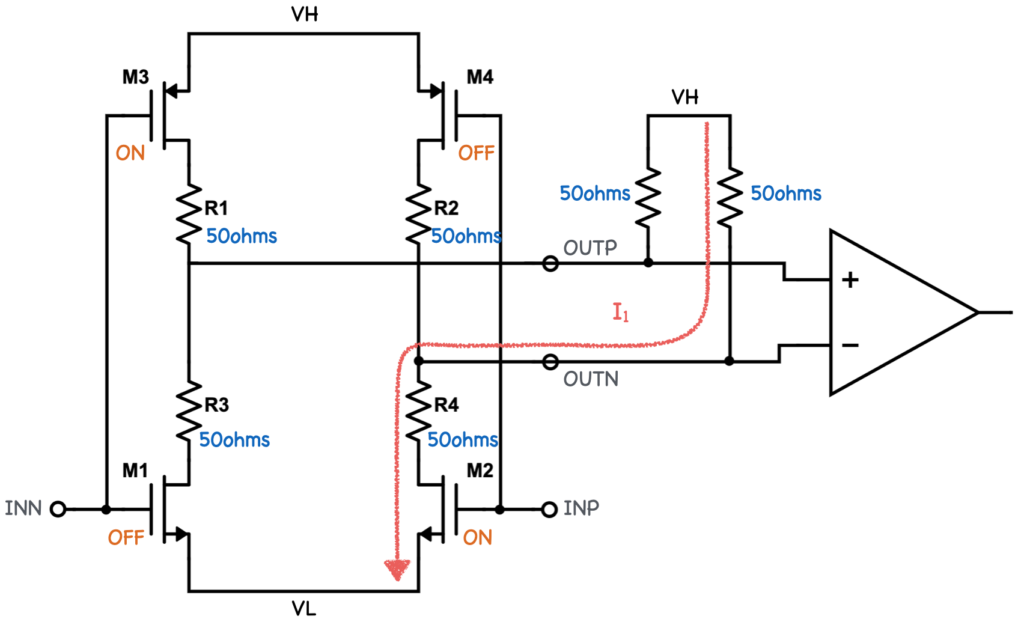

LVDSのアーキテクチャは幾つかバリエーションがあるようですが、論文等でよく見るのは下図の上下に電流源がついているタイプです。

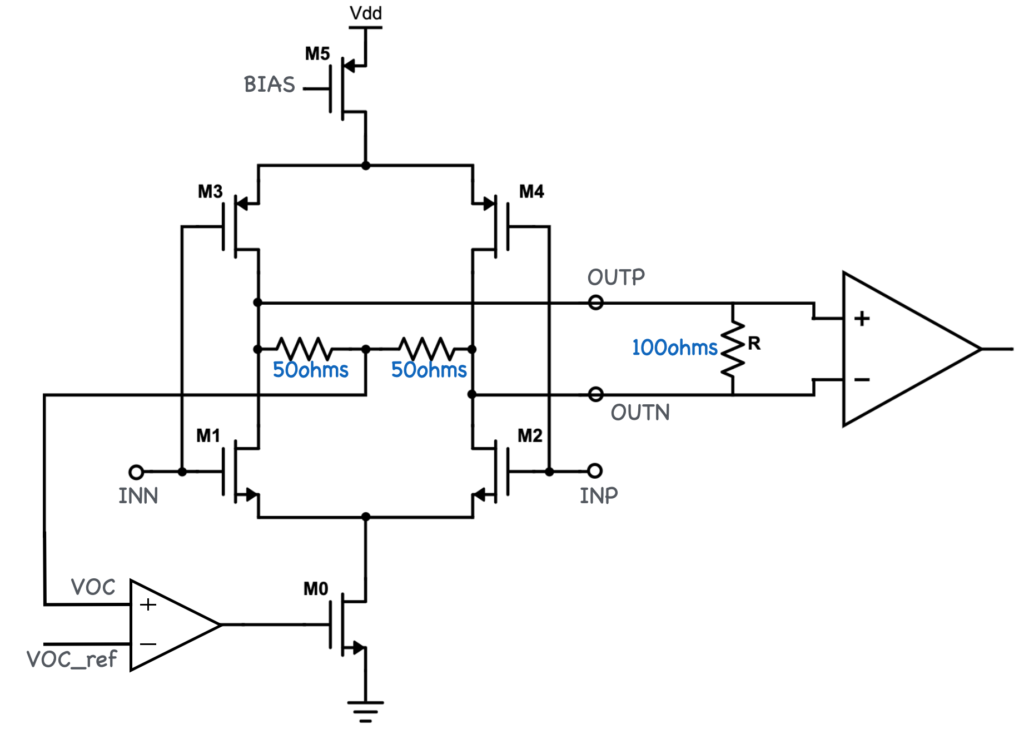

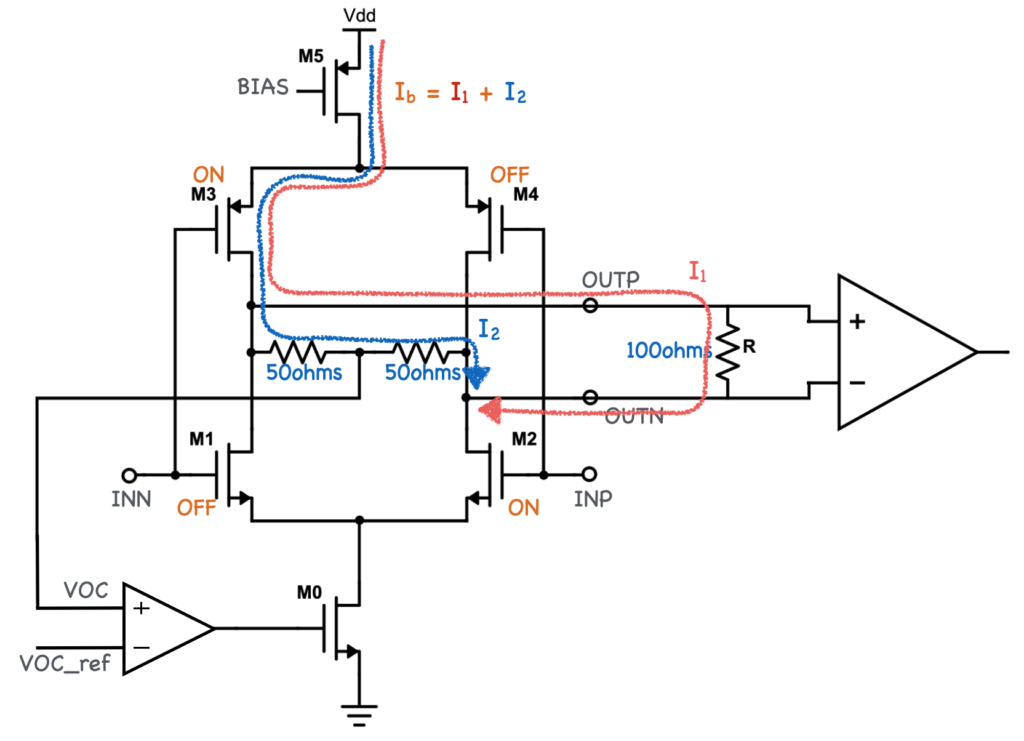

$M0$と$M5$は電流源として動作し、$M1\sim M4$はスイッチとして動作します。出力インピーダンスは差動では内部抵抗により100ohmsでインピーダンス整合がとれています。一方で同相インピーダンスはHighZであり、$V_{OC}$を決定するためにはコモンモードフィードバックが必要になるため、同相出力電圧を$M0$電流源のゲートにフィードバックしています。CMLと同様に$M5$電流源は所望の$V_{OD}$を得るために適切にバイアスされる必要があります。

バイアス電流$I_b$は内部抵抗100ohmsと受信側終端抵抗100ohmsで等しく分流され、出力振幅としては$V_{OD}=\frac{I_b}{2}*100\Omega$が得られます。これは同じ$I_b$に対してCMLの2倍の振幅が得られることになります。言い換えるとLVDSはCMLの半分の消費電流で同じ$V_{OD}$を得ることができます。一方で、上下に電流源があるため動作点的に大振幅を出力することはCMLと比較して難しくなります。

LVDSの特徴は、

- 出力振幅は$V_{OD}=I_b*50\Omega$。

- 定電流のため$dI/dt$ノイズが小さい。

- 内部抵抗で出力抵抗が決まるためインピーダンス整合が取りやすい。

- 上下ともに電流源のため、PSRRが良い。

- 同相出力電圧$V_{OC}$を自由に決められる(バイアス電流とは無関係)。

- 電流源の動作点確保のため出力振幅$V_{OD}$を大きくできない。

- 出力振幅に直接影響するためバイアス電流の精度が重要。

VML (Voltage Mode Logic)

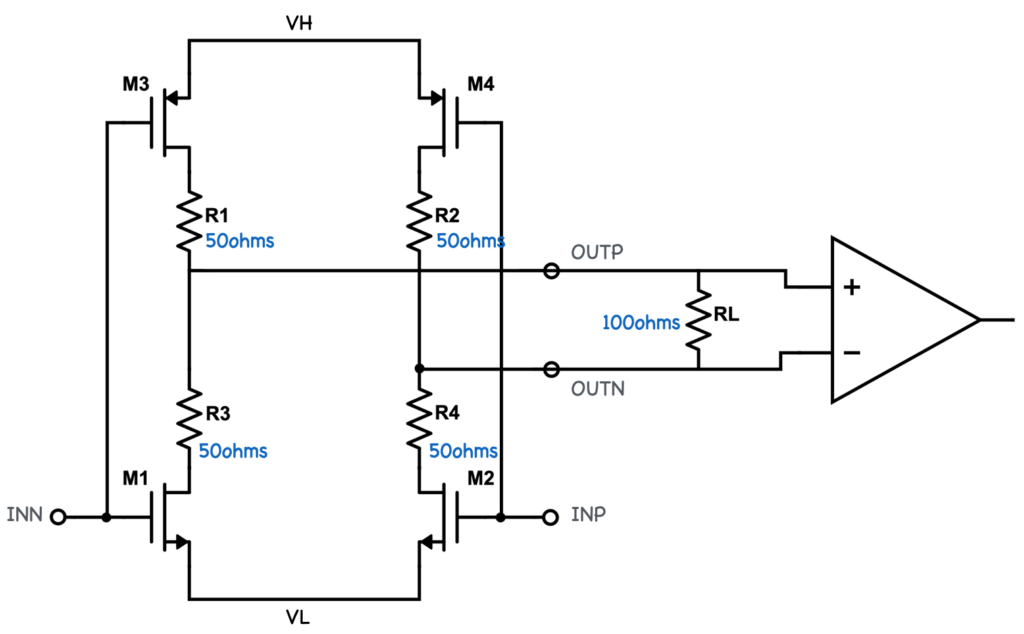

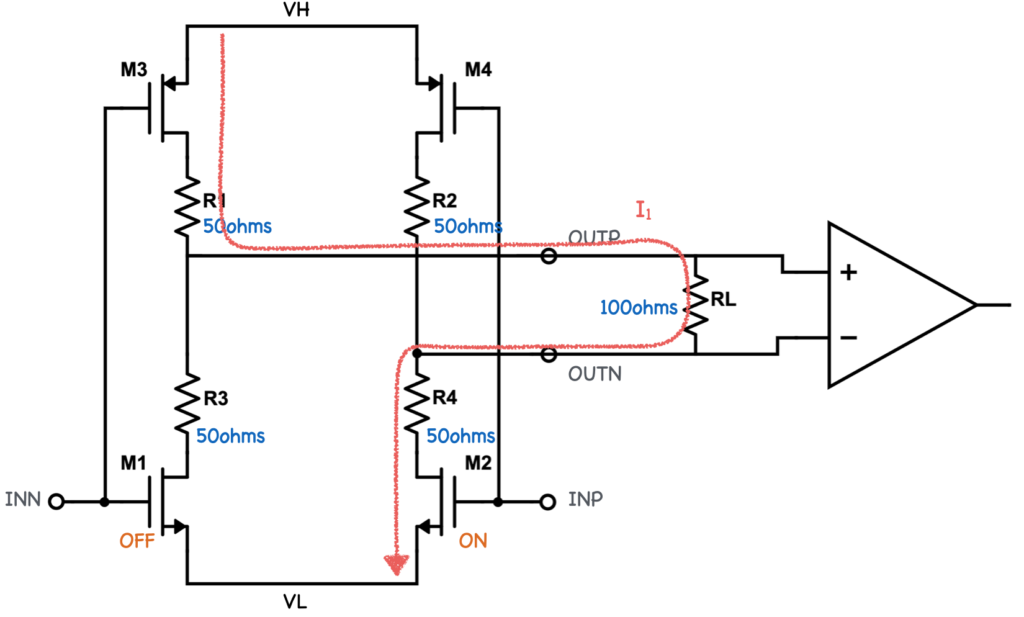

VMLは電圧駆動型のアーキテクチャです。CMLやLVDSと異なって電流源は不要で、$M1\sim M4$の全てのMOSは低抵抗のスイッチとして動作します。内部抵抗$R1\sim R4$に直列にMOSスイッチが繋がるので、インピーダンス整合をとるためには各MOSの抵抗は50ohmsに比べて十分小さくなければならず、大きいMOSサイズが要求されます。これはMOSスイッチを駆動するPre-driverのサイズ、消費電流の増加に繋がってしまいます。

Differential Termination

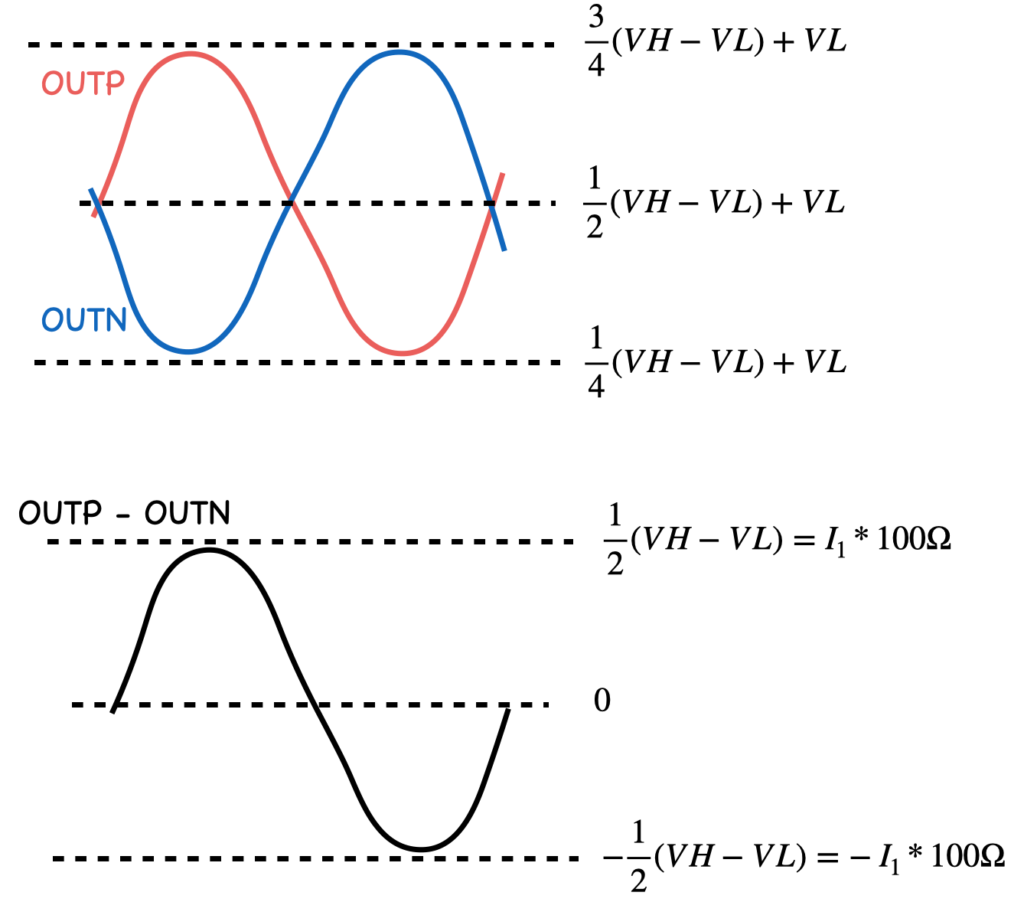

差動出力電圧$V_{OD}$は$VH$と$VL$を内部抵抗と受信側終端抵抗$RL$で抵抗分圧したものとなります。出力段の消費電流$I_1$は全て$RL$に流れ込むので$V_{OD}=I_1*100\Omega$となり、消費電流はCMLの4分の1で済みます。抵抗分圧のため基本的に$V_{OC}$は$(VH+VL)/2$で固定であり、$V_{OD}$は$(VH-VL)/4$が最大となります。また、スイッチ切り替え時に全てのMOSがオンする可能性があり、シュートスルー電流として大電流が流れないよう注意が必要です。

Single-Ended Termination

この場合の出力振幅は$V_{OD}=I_1*50\Omega$なので消費電流がDifferential Terminationの2倍となります。

VML(Differential Terminationの場合)の特徴は、

- 出力振幅は$V_{OD}=I_1*100\Omega$であり消費電流が小さい。

- 電流源を持たないのでバイアスが不要。

- 同相出力電圧はVH, VLに依存して$V_{OC}=(VH+VL)/2$。

- 最大差動出力振幅が小さく$V_{OD}=(VH-VL)/2$

- インピーダンス整合のためにMOSサイズを大きくする必要があり、Pre-driver電流が大きい。

- シュートスルー電流に注意する必要あり。

比較とまとめ

以下に各アーキテクチャの特徴をまとめました。

VMLはCMLに比べて出力段の消費電流が4分の1と小さいのが利点ですが、実際には出力段に加えてPre-driver、エンファシス、バイアス回路、スルーレート制御回路などの消費電流が加わります。特にVMLではスイッチの容量が大きいためにPre-driverの消費電流が増加し、全体の消費電流に大きく寄与するので注意が必要です。

CMLは電流が大きい一方で大振幅を出せるのが特徴です。電流のばらつきが出力電圧のばらつきとなるので、エンファシス設定などに依らず内部電圧を一定にバイアスするなどしてばらつきを抑える工夫が必要です。

LVDSの1番の特徴は$V_{OC}$を任意に決定できるということかもしれません。CMLやVMLで$V_{OC}$を調整するにはバイアス電流や電源電圧を変える必要がありますが、これらは$V_{OD}$に直接影響してしまいます。LVDSでは$V_{OD}$とは無関係に$V_{OC}$を設定できます。

Users Today : 69

Users Today : 69 Total Users : 272520

Total Users : 272520

コメント