CMOSカレントミラーの基本原理について説明します。

実際にどのようなアーキテクチャがあるかについては、CMOSカレントミラーの構成まとめにまとめていますのでこちらもあわせて見てみてください。

概要

アナログ回路ではBGRなどのバイアス生成回路から供給される参照電流をコピーして分配することで、各回路を精度の良い電流でバイアスすることができます。この電流のコピーを実現するのがカレントミラー(Current Mirror)で、アナログ回路設計において基本的かつ重要なものです。

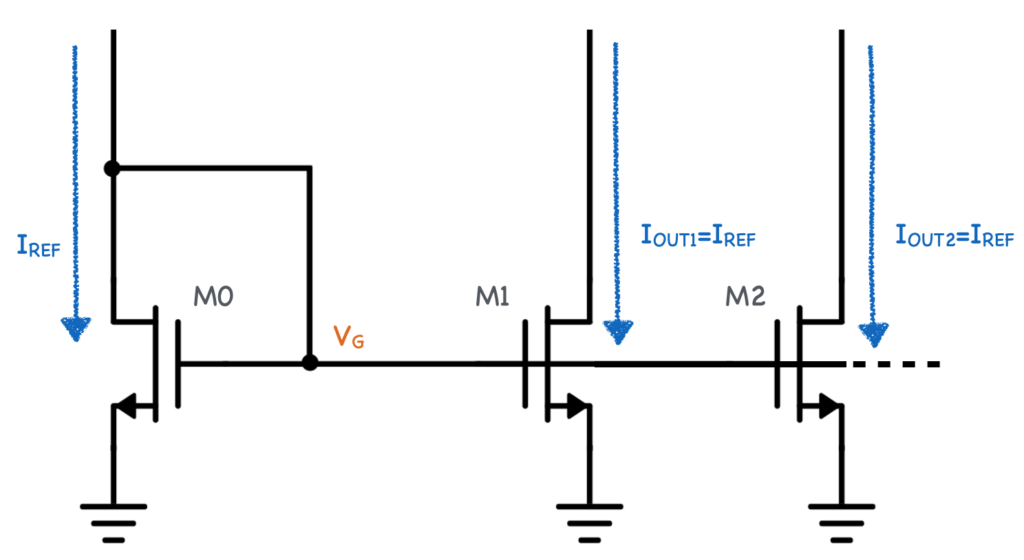

下図はNMOSを使った基本的なカレントミラーです。

$M0$に参照電流$I_{REF}$が入力されることでゲート電圧$V_G$が決定され、これを$M1$のゲートに入力することで$I_{REF}$と同じ値の電流がコピーされて$I_{OUT1}$として出力されます。

バイポーラとは異なりMOSFETはゲートに直流電流を流さないため、上図のように1つの$I_{REF}$から複数の電流をコピーすることができます。

また、電流の完全なコピーだけではなくMOSのサイズ比に比例して電流量を増減させることも容易に可能です。

原理

電流源のMOSは必ず飽和領域で動作させます。飽和領域にあるMOSは、電流のドレイン・ソース電圧($V_{DS}$)依存が小さい、言い換えると出力抵抗が大きいためです。

一般的に電流源は出力抵抗が大きいほど出力電圧の変動に対して電流値の変動が小さく、より理想的な電流源として振舞います(完全に理想的な電流源の出力抵抗は無限大)。

飽和領域でのMOSのドレイン電流$I_D$は以下のようにモデル化されます。

$$I_D=\frac{1}{2}\mu C_{ox}(V_{GS}-V_{TH})^2(1+\lambda V_{DS})$$

ここで、$L$はゲートの長さ、$W$はゲートの幅、$\mu$はキャリアの移動度、$C_{ox}$は単位面積あたりのゲート容量、$V_{GS}$はゲート・ソース間電圧、$V_{TH}$は閾値電圧、$\lambda$はチャネル長変調効果の補正項です。このうち設計者が自由に調整できるのは$L$と$W$のみで、残りはプロセスに依存します。

この式から$I_{REF}$と$I_{out1}$は

$ I_{REF}=\frac{1}{2}\mu C_{ox} \frac{W_0}{L_0}(V_{GS0}-V_{TH})^2(1+\lambda V_{DS0}) $

$ I_{OUT1}=\frac{1}{2}\mu C_{ox} \frac{W_1}{L_1}(V_{GS1}-V_{TH})^2(1+\lambda V_{DS1}) $

と表され、$V_{GS0}=V_{GS1}$なので、

$$I_{OUT1}=\frac{W_1/L_1}{W_0/L_0} \frac{(1+\lambda V_{DS1})}{(1+\lambda V_{DS0})} I_{REF}$$

となります。

ここでチャネル長変調効果が十分小さく$\lambda V_{DS}\ll 1$とすると、

$$I_{OUT1}=\frac{W_1/L_1}{W_0/L_0} I_{REF}$$

となり、プロセスや温度とは無関係に$L$と$W$の比のみをパラメータとして電流をコピー(ミラー)することができます。

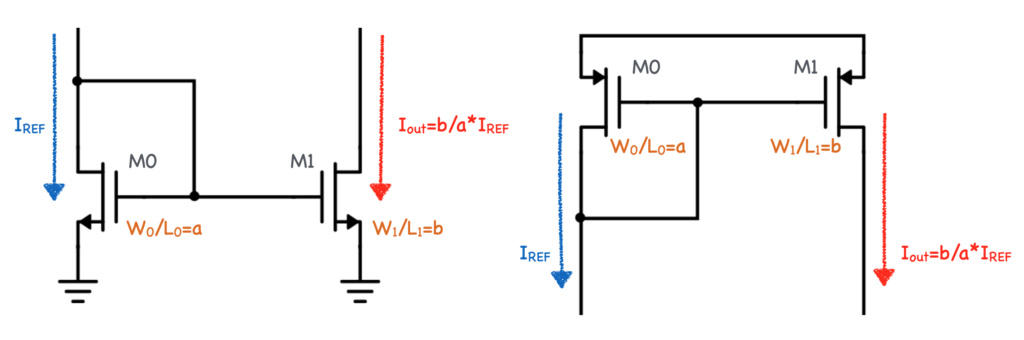

たとえば下図の例ではバイアス回路から供給された$I_{REF}$をちょうど$b/a$倍の電流にコピーして$I_{out}$として出力しています。

もしミラー元の電流源の$V_{DS0}$とミラー先の電流源の$V_{DS1}$に差があれば、チャネル長変調効果による補正項の違いによりコピーされる電流に大きな誤差が生じてしまいます。そのため、電流精度が必要な部分ではカスコードカレントミラー構成にするなどしてチャネル長変調効果を抑える工夫をします。詳しくはCMOSカレントミラーの構成まとめを見てみてください。

回路設計上の注意

実際に回路設計を行う際には、電流を正確にコピーするために気を付けるべき点があります。

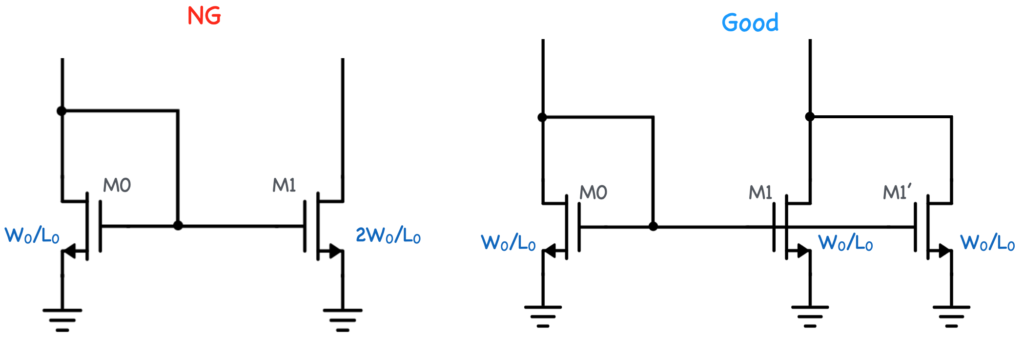

第一に、ミラー元と同じサイズのMOSをミラー先で使う必要があります。例えば下図のように参照電流のちょうど2倍の電流を出力したいとき、$M1$の$W$を2倍にしたのでは正確なコピーはできません。これは実際に製造された際にはゲートの端の分だけ有効ゲート幅が小さくなり、$M0$の有効ゲート幅は$W_{eff0}=W_0-W_{d}$であるのに対して、$M1$のそれは$W_{eff1}=2W_0-W_{d}\neq 2*W_{eff0}$となり2倍にはならないためです。正確なコピーのためには下図右のように全く同じ寸法のMOSを並列に並べます。

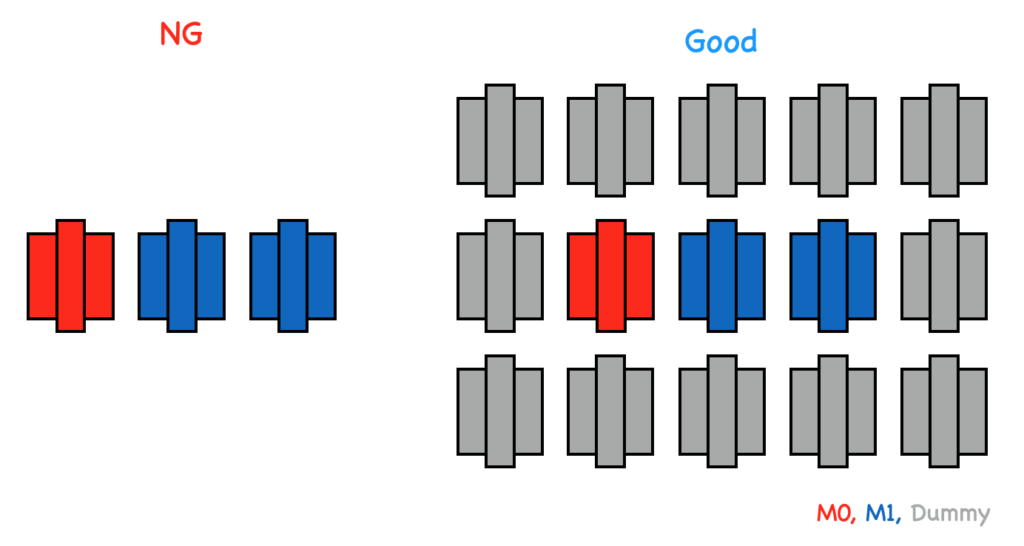

第二に、レイアウト時にミラー元MOSとミラー先MOSを周辺環境を含めて等しくするということです。下図左では$M0$と$M1$に周辺回路から加えられる物理的なストレスが異なるため電流のミスマッチが生じてしまいます。これを避けるため素子周辺にダミーの素子を置き、周辺環境をミラー元とミラー先で等しくします。

コメント